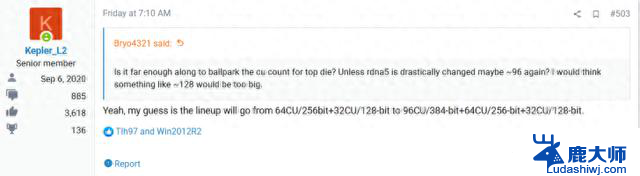

AMD下代显卡曝光,至高96CU配置挑战英伟达旗舰

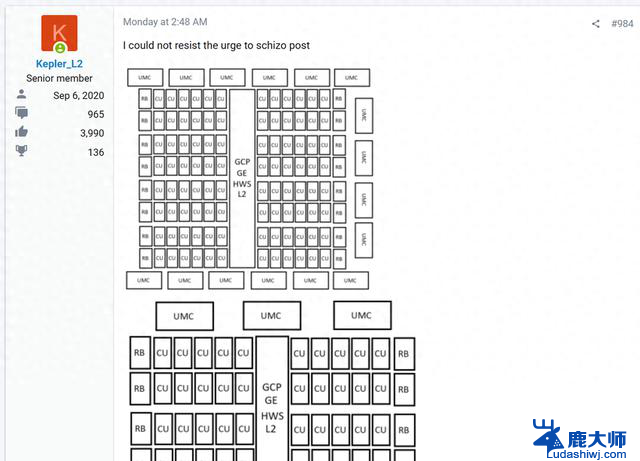

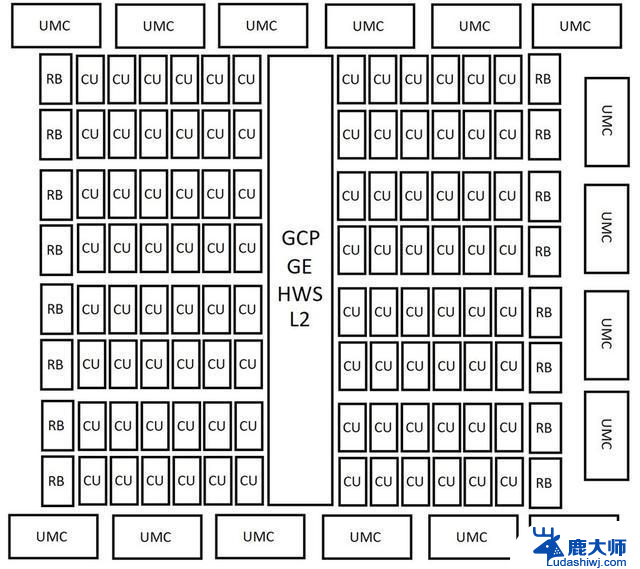

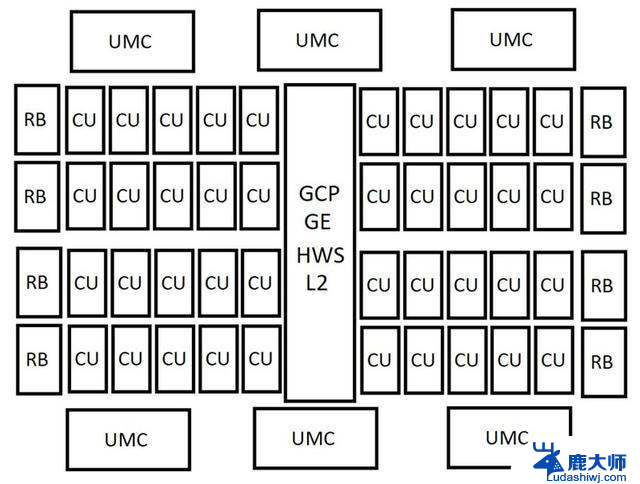

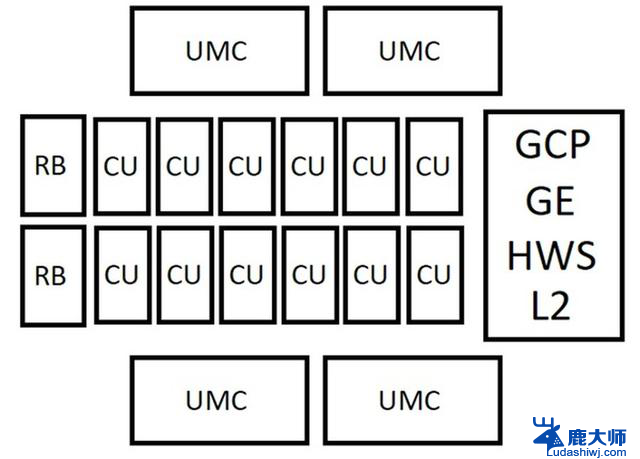

知名爆料人Kepler_L2在AnandTech论坛上发布了这四种核心的设计示意图,具体的配置信息和对应图片如下:

AT0,拥有8个着色器阵列 / 16个着色引擎(每组着色器阵列有2个着色引擎)/ 96个CU(每个着色引擎有6个CU)/ 位宽512-bit(16个32-bit显存控制器)/ Infinity Cache最多为128MB。

AT2,拥有4个着色器阵列 / 8个着色引擎(每组着色器阵列有2个着色引擎)/ 40个CU(每个着色引擎有6个CU)/ 位宽192-bit(6个32-bit显存控制器)/ Infinity Cache预计为48MB。

AT3,拥有2个着色器阵列 / 4个着色引擎(每组着色器阵列有2个着色引擎)/ 24个CU(每个着色引擎有6个CU)/ 位宽128或256-bit(8个16或32-bit显存控制器)/ Infinity Cache可能是32MB。

AT4,拥有1个着色器阵列 / 2个着色引擎(每组着色器阵列有2个着色引擎)/ 12个CU(每个着色引擎有6个CU)/ 位宽64或128-bit(4个16或32-bit显存控制器)/ Infinity Cache可能是16MB。

AMD在最近的Hot Chips 2025上,暗示UDNA架构可能采用模块化的设计,以提供更为灵活的配置方案。而结合上述配置来看,AT3的显存控制器数量甚至比高一级的AT2还要多,结合近日有传闻说AT3和AT4将引入LPDDR6/5X, 取代GDDR作为显存,推测可能与这个改动有关。